# 規格書 Data Sheet

**CUSTOMER:**

**Basler**

Model NO:

U3X4-PCIE4XE111

**DESCRIPTION:**

Quad Channel 4-port USB 3.0 PCI Express x4 Gen 2 Host Card

Revision:

**1.1.2** Date: 2023/5/29

CUSTOMER APPROVAL ENGINEER ISSUE BY

映奥股份有限公司

新北市新店區寶橋路235巷125號4樓

4F, No.125, Lane 235, Baociao Rd, Sindian Dist,

New Taipei City 231, Taiwan, R.O.C.

TEL: 02-89191358 FAX: 02-89191359

# Content

## Overview:

| 3 |

|---|

| 3 |

| 4 |

| 4 |

| 4 |

|   |

| 5 |

| 5 |

|   |

| 6 |

|   |

| 7 |

|   |

| 8 |

|   |

#### Overview:

#### Introduction

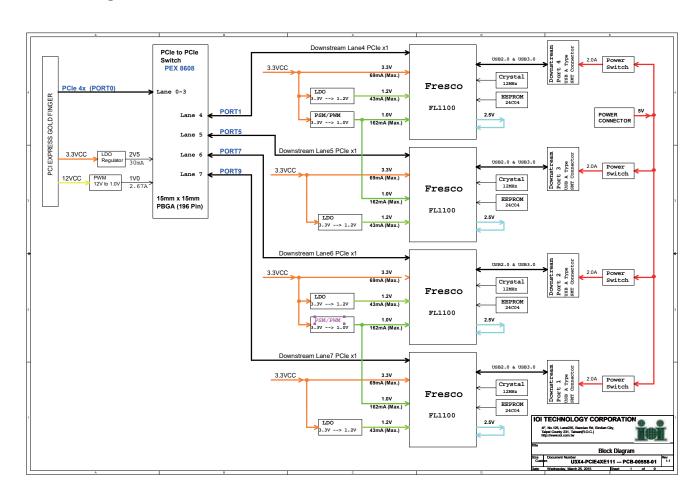

The U3X4-PCIE4XE111 is a Quad channel USB 3.0 to PCI Express x4 Gen 2 Host Adapter.

U3X4-PCIE4XE111 is designed with Two key components.

- 8-Lane, 8-Port PCI Express Switch.

- PCI Express to USB 3.0 Single Chip Host Controller (Fresco FL1100, USB IF TID 380000026).

Utilizing the standard PCI Express Switch, the 8-Lane/8-Port PCI Express Switch provides the most efficient fan-out solution for integrating four PCI Express to USB 3.0 Single Chip Host controllers into a small board design. Each USB 3.0 to PCI Express Single Chip Host controller takes advantages of 5 Gbps burst rate of 4-lane PCI Express bus in both directions and is fully compliant with PCI Express Base specification r2.0. This solution provides full PCI Express and USB 3.0 functionality and performance.

### **Technical Specifications**

#### **Primary PCI Express**

- Standards compliant

- PCI Express Base Specification r2.0 (Backwards compatible with PCIe r1.0a/1.1)

- PCI Power Management Spec r1.2

- Microsoft Vista®-compliant

- Supports Access Control Services

- Dynamic Link-width control

- Dynamic SerDes speed control

- High Performance

- Non-Blocking Internal architecture

- Full line rate on all Ports

- Cut-Thru latency: 130ns

- 2KB max payload size

- PCI Express Power Management

- · Link power management states: L0, L0s, L1, L2/L3 Ready, and L3

- Device states: D0 and D3hot

- Quality of Service (QoS) support

- Two Virtual Channels (VC) per Port

- Eight Traffic Classes per Port

- Weighted Round-Robin Port & VC Arbitration

#### **Secondary PCI Express**

- Four Single (x1) PCI Express Lane

- Supports PCI Express Specification Revision 2.1 at 5GT/s

- Supports PCI Bus Power Management Interface Specification revision 1.2

- Support for Latency Tolerance Reporting (PCIe)

#### **USB Features**

- Compliant with USB 3.0 Specification Revision 1.0

- Compliant with Extensible Host Controller Interface (xHCI) Specification revision 1.0

- 4 downstream USB ports support SS/HS/FS/LS data rates (5Gbps/480Mbps/12Mbps/1.5Mbps)

- Supports UASP (USB Attached SCSI Protocol)

- Supports xHCl debug capability

- Support for Ultra High-performance isochronous applications

- Support for Latency Tolerance Tolerance Messaging (USB)

#### **Advanced Power Saving**

- Support all USB 3.0 Power States: U0, U1, U2 and U3

- Support USB 2.0 Link Power management (LPM) •USB-IF LPM PDK Standard

- PCIe Active State Power Management (ASPM) L0s and L1

#### **USB3** cable lock mechanism

vides the threaded holes for the jack-screws of

**USB Bus Power Input**

USB 3.0 A Plug w/Jackscrew lock Cable

5V from either ATA 4-pin Power Connector (J1) or/and SATA 15pin Power Connector (J2)

#### **Storage Temperature**

• 0°C to 70°C(32°F to 150 °F)

#### **Storage Humidity**

• 10% to 80% (Non-Condensing)

## **Computer Platform**

Computer with PCI Express slot (x4, x8, x16)

#### Note:

For the best performance (5.0 Gbps), It should be installed in a PCle Gen 2 compliant slot in the host computer. A PCle Gen 1 compliant slot reaches up to 2.5 Gbps throughput

## **Operating System Requirements**

- If OS is Windows 8 or later , there are inbox driver for Fresco USB 3.0 Host Controller.

- · Linux xHCl support under Linux kernel version 2.6.31 and after

- USB 3.0 Host Drivers

- · Windows XP

- Windows Vista

- Windows 7

- Windows 8 and 8.1

## **Block Diagram**

# Silk Screen and Picture:

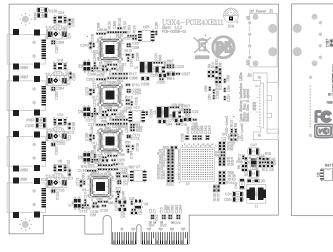

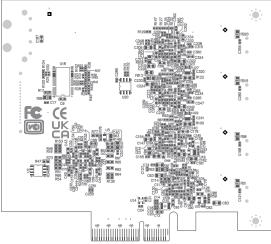

# Silk Screen of U3X4-PCIE4XE111 P.C.B (PCB-00558-02)

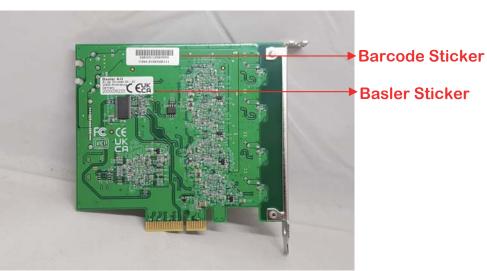

## Picture of U3X4-PCIE4XE111 PCBA

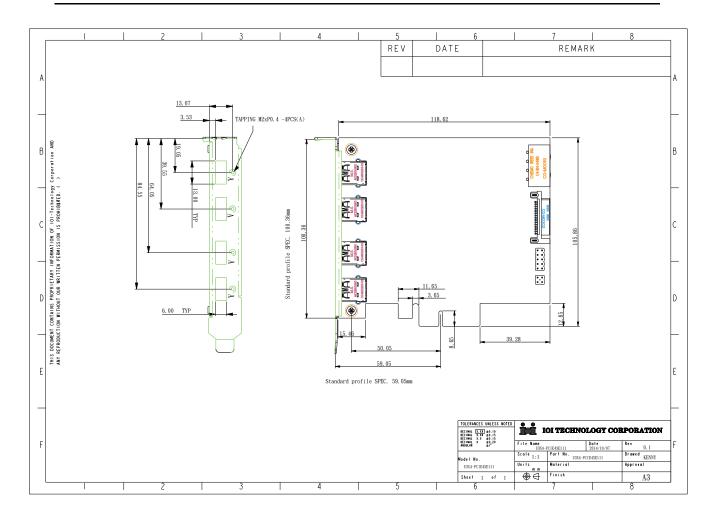

# **Mechanical Dimension:**

## **Kit Parts Information:**

# Datasheet of USB 3.0 host controller USB IF TID 380000026

#### FL1100-1Q0-EX

PCI Express to 4-port USB 3.0 Host Controller

#### Introduction

The FL1100 is Fresco Logic's single-chip PCI Express to USB 3.0 host controller. It fully integrates an Extensible Host Controller Interface (xHCI) engine, a 4-port 5Gbps USB 3.0 transceiver, a PCI Express endpoint controller and a 5Gbps PCI Express transceiver. FL1100 implements the Universal Serial Bus 3.0 Specification Revision 1.0 and the Extensible Host Controller Interface (xHCI) Specification Revision 1.0, and complies with the PCI Express Rev 2.1 Specification at 5Gbps data rate, and is backward compatible to the PCI Local Bus Specification Revision 2.2. FL1100 is compatible for operation with USB 2.0 and USB 1.1 devices. The FL1100 controller features Fresco Logic's patented GoXtream™ xHCI Accelerator Engine, which maps the xHCI standard directly into a set of parallel functional units, providing acceleration of all xHCI operations while maintaining compatibility with existing software driver models.

The FL1100 supports USB Debug Capability defined by the xHCl specification. Debug capability enables low-level system debug using a USB-to-USB connection between two computers, and is a requirement from Microsoft for those platforms that wish to achieve Windows Logo Certification for Windows 8 and beyond.

With its innovative architecture and high level of integration, FL1100 delivers exceptional performance, while minimizing total system cost and providing the most straightforward usage model in the industry.

#### **Feature**

- Compliant with USB 3.0 Specification Revision 1.0

- Compliant with Extensible Host Controller Interface (xHCI) Specification Revision 1.0

- 4 downstream USB ports support SS/HS/FS/LS data rates (5Gbps/480Mbps/12Mbps/1.5Mbps)

- Supports Battery Charging Specification Revision 1.2 for Charging Downstream Ports (CDP)

- Supports USB charging via Chinese Telecom Standard YD/T 1591-2009

- Supports Apple™ Charge

- o Single (x1) PCI Express Lane

- Supports PCI Express Specification Revision 2.1 at 5GT/s

- Supports PCI Express Card Revision 1.0

- ° Supports PCI Bus Power Management Interface Specification Revision 1.2

- 3.3V/1.2V/1.05V power supply

- Supports 12MHz crystal oscillator

- Integrated SuperSpeed USB transceiver

- Integrated PCI Express transceiver

- WHQL certified driver support for Windows 8, Windows 7, Windows Vista and Windows XP

- Linux xHCl support under Linux kernel version 2.6.31 and after

- · Supports UASP (USB Attached SCSI Protocol)

- Supports xHCl debug capability

- Support for Ultra High-performance isochronous applications

- Support for Latency Tolerance Reporting (PCIe) and Latency Tolerance Messaging (USB)

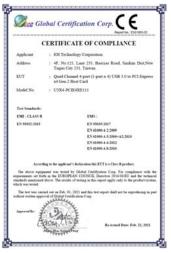

# **Certifications & Compliances:**

CE Test: Pass UKCA Test: Pass FCC Test: Pass VCCI Test: Pass

| Model No.       | RoHS<br>(2011/65/EU<br>& 2015/863) | EU RoHS<br>Exemption | US TSCA   | Reach SVHC Contained | Reach SVHC | Note            |

|-----------------|------------------------------------|----------------------|-----------|----------------------|------------|-----------------|

| U3X4-PCIE4XE111 | Compliant                          | 7c-l                 | Compliant | No<br>※Note 2        | Compliant  | Re Series: 7c-i |

**Note 2:** Some electronic components contain lead under the permission of RoHS exemption (7C-I) in a glass or ceramic. REACH ECHA is not applicable for articles containing glass and ceramics since they are classified under REACH as UVCB substances (substance of unknown or variable composition, complex reaction products or biological material).

This information is provided to the best of our current actual knowledge based on information provided by our third-party suppliers in response to our reasonable inquiries. We make no representation or warranty and assume no liability for the accuracy of, information supplied by third parties.